AVVENTURA SOFTROCK.

SECONDA PUNTATA

RICEVITORE SDR ENSEMBLE III

SEGNALI IQ

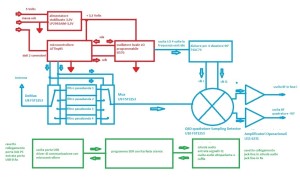

Continuiamo la discussione dello schema a blocchi del ricevitore. Nella precedente puntata abbiamo discusso la zona rossa. La parte controllata dalla porta USB che non ha nulla a che fare con la parte RADIO vera e propria. La parte RADIO è la zona blu che tratta il segnale a radio frequenza in modo analogico e produce i due segnali in quadratura in banda base da inviare alla scheda audio del PC. Guardiamo lo schema a blocchi.(clicca sopra per ingrandire)

Prendiamo in considerazione la zona blu con i relativi blocchi e collegamenti.

Da sinistra a destra. I segnali radio indotti nell’antenna entrano attraverso il connettore coassiale tipo BNC, raggiungono il DeMux U8 FST3253 tramite un trasformate e due diodi limitatori. La posizione del DeMux dipende dalla sequenza proveniente dal Microcontrollore ATTiny85 della zona rossa esaminato nella prima puntata. La sequenza di commutazione arriva tramite due Optoisolatori, U4 LTV-817 non disegnati nello schema a blocchi, per separare elettricamente la zona rossa parte USB dalla zona blu parte RADIO. Le quattro posizioni del DeMux selezionano i filtri di banda corrispondenti alla frequenza centrale scelta nell’interfacia utente nel PC. Per i limiti di banda e sequenza di commutazione, fare riferimento alla tabella pubblicata nella prima puntata.

I primi due filtri di banda, corrispondenti alle due bande inferiori, sono attenuati da un filtro pigreco resistivo. Nel terzo filtro di banda i segnali transitano in maniera passiva. Il quarto filtro, relativo alla banda più alta, i segnali sono amplificati da un BJT NPN. Il secondo commutatore elettronico funziona da Mux è uguale a U8 ma funziona al contrario riferendoci alle entrate e alle uscite. U9 FST3253 è comandato in parallelo al precedente, sono sincronizzati. All’uscita del Mux U9 abbiamo i segnali radio della sola porzione di banda HF selezionata dai due commutatori elettronici e relativi filtri.

Dall’oscillatore locale LO, zona rossa, arriva il segnale per mezzo di un trasformatore T1 che separa galvanicamente e elettricamente le due zone. Tale segnale, quattro volte superiore alla frequenza centrale della finestra di ricezione nell’interfacia utente, è il clock che comanda il divisore U7 74AC74. Questo integrato contiene due latch tipo D, il clock è attivo nella rampa di salita, nelle uscite barrate /Q dei dispositivi sequenziali, preleviamo due segnali ad onda quadra perfettamente uguali ma sfasati di 90°, appunto in quadratura.

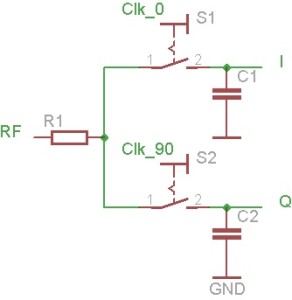

Lo stadio QSD Quadrature Sampling Detector usa un integrato FST 3253 U10, trasforma i segnali a radio frequenza in segnali in banda base. Nonostante il nome (Detector) non è un rivelatore. Non è neppure un convertitore sebbene ci sia un cambiamento di frequenza. Non è neppure un convertitore ADC anche se lavora come un Sampling & Hold (Campiona e mantieni). Dan Tayloe/N7VE, il suo inventore, lo ha pensato, nella forma più elementare, la nostra, come due interruttori che caricano due condensatori.

Nella figura lo schema elettrico è semplificato al massimo. Il segnale RF attraverso R1 arriva ai due interruttori comandati dai due segnali onda quadra di clock provenienti dal divisore. La chiusura avviene nella rampa di salita quando il segnale di clock raggiunge il massimo e restano chiusi per tutto il tempo in cui il clock resta al massimo. Si aprono appena inizia la rampa di discesa.

Quando S1 si chiude, comandato dal clock in fase I, nella figura indicato come Clk_0, si carica il condensatore C1 secondo la costante di tempo t=R*C, t è il tempo richiesto per caricare o scaricare il condensatore attraverso R1. S2 si chiude comandato dal segnale di clock sfasato di 90° Q nello schema Clk_90. Ai capi di C1 e C2 avremo due segnali, in banda base, identici fra di loro ma sfasati di 90°.

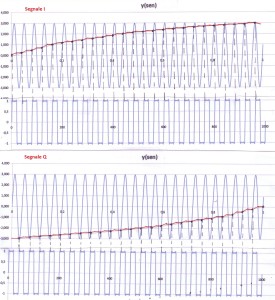

La tabella seguente mostra nei dettagli come avviene il processo di produzione dei segnali IQ .(cliccarci sopra per ingrandire e poi con lente sopra al grafico e tasto sinistro per ingrandire ulteriormente)

La tabella mostra come avviene la transizione di un segnale ricevuto a 2525 Khz, segnale sinosuidale, in segnale in banda base(bassa frequenza) sia per il segnale I che per il segnale Q.

I segnali in banda base sono disegnati con tratto rosso. Le linee verticali tratteggiate rappresentato l’istante preciso in cui si chiude l’interruttore e avviene in campionamento del segnale che dura fino all’apertura dell’ interruttore. Dopo di che il condensatore mantiene la carica fino alla prossima chiusura dell’interruttore. I due segnali IQ in banda base, tratto rosso, sono anche loro in quadratura.

La frequenza centrale di 2500khz è rappresentato dalle due onde quadre provenienti dal divisore, il secondo segnale a onda quadra, l’ultimo in basso, è spostato leggermente a sinistra rispetto all’asse Y del piano cartesiano perché è sfasato di 90°. I due segnali sinusoidali in effetti sono solamente uno ma per praticità di rappresentazione ho preferito disegnarne due per rendere il grafico più chiaro. Il modello rappresentato non rispecchia condizioni reali di lavoro del QSD. Ho cercato simulare graficamente l’operatività del dispositivo.

Riepilogando, la frequenza di campionamento è 2500 khz(onde quadre) mentre la frequenza campionata, la frequenza di ricezione, è 2525 khz (onda sinusoidale) c’ è la differenza di 1%. Il segnale viene campionato con 1 centesimo di ciclo di anticipo per ogni ciclo.

Visto che il QSD opera come un Sample & Hold, bisogna fare una considerazione riguardo il Teorema di Campionamento di Nyquist-Shannon che recita: per campionare un segnale senza perdita di informazione, bisogna campionarlo con frequenza almeno doppia della più alta componente spettrale del segnale.

Nel nostro caso la frequenza di campionamento è molto vicina alla frequenza campionata. Non viene rispettato il teorema di Nyquist-Shannon. Il QSD lavora in regine di sottocampionamento incorrendo nel fenomeno di Aliasing che nel caso di ADC (Analogic Digital Converted) produrrebbe distorsione. Ma poiché, nel nostro caso, non vi è conversione Analogico-Digitale, il sottocampionamento viene sfruttato a nostro favore.

La puntata termina qui.

La prossima discussione riguarderà gli amplificatori operazionali.

I3fdz/Fiorino

La mia attività di Radioamatore consiste nella caccia al dx, partecipazione a Contest nazionali e internazionali in HF, ricerca e restauro di apparati storici Vintage.

La mia attività di Radioamatore consiste nella caccia al dx, partecipazione a Contest nazionali e internazionali in HF, ricerca e restauro di apparati storici Vintage.